実験回路

NANDゲート(74HC00)を使用したセラミック発振回路からサイン波を取り出す実験です。

ゲート出力-発振子間に挿入した抵抗の発振子側は、サイン波に近い波形であることが分かりました。ここからサイン波を取り出しています。

NANDゲートを使用した理由は発振のON/OFF制御を行いたいためです。

インバータを使用した水晶/セラミック発振回路のサイン波形に関して調査したところ2件の情報がありました(*)。何れも、インバータの『入力側』が発振子の自由振動波形であることを述べています。

( * : ①「ほんとに使える電子回路教科書 第9章」トラ技 2012年5月 ②「水晶振動子とは」RSエレクトロニクスセンター技術情報 )

<2014.04.10 追記>

更に情報を得ました。web上で「フランクリン型発振」を調べていてヒットしたものです。

1)「すzのAVR研究 フランクリン型発振回路」(ブログ 2007年7月)

以下の2)及び3)を紹介しています。

2)トランジスタ技術 2003年8月号(CQ出版 馬場清太郎)

3)トランジスタ技術 SPECIAL OPアンプによる実用回路設計(CQ出版 馬場清太郎著)

2)〜3)においてサイン波を安定して得るためにインバータ出力に抵抗が必要であることが記述されています。

3)においてHCU04による水晶発振回路により綺麗なサイン波が得られることを述べておられます。この波形(写真)はインバータの入力側でした。但し、他の回路(インバータを使用したLC発振回路)では、インバータ出力から抵抗を介した箇所を出力としています。

<2014.04.14 追記>

更に情報を得ました。前回改版日(2014.04.10)に発売されたトラ技です。

1)トランジスタ技術 2014年5月号(CQ出版 馬場清太郎)

上の2)〜3)の回路と同じですが、取り出し箇所がインバータ出力から抵抗を介した箇所となっています。

これまで入手した情報から本章公開の意味はほとんど無くなりましたが、測定データ等は参考にはなるかと思い、記載内容の削除、修正等は行わないことにします。

『入力側』がサイン波となることは分かりましたので、『出力側』ではどうか実験しました。但し、発振回路にはインバータではなくNANDゲート(74HC00)を使用しています。

『出力側』の波形を観測したところ、オーバートーン発振や異常発振を防止するための抵抗を通した箇所は、サイン波に近い波形となることが分かりました。

以下、波形測定と負荷接続による影響ついて調査しています。結果、周波数可変の用途には、振幅変動の少ない『出力側』からの取り出しが有効であることが分かりました。

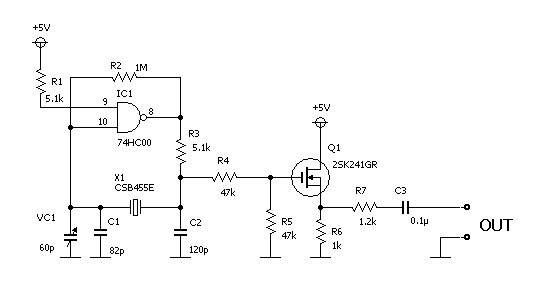

実験回路を下図に示します。

波形確認箇所は入力側「A」点と出力側「B」点です。但し、実際には、それぞれ、「MON A」および「MON B」から測定しています。「MON A」側のC3およびR5は、プローブ(10pF,10MΩ)接続時の不安定動作防止のために設けています。C3はバイアスDCカット用です。

「MON」は周波数測定に使用します。

RLは取り出し回路接続による影響を調べるための擬似負荷で、「接続負荷の影響」調査時のみ接続します。

R2は本来、オーバートーン発振や過大励振レベルによる異常発振の防止用ですが、今回の実験ではサイン波に近い波形を得るために使用しています。本来の目的とは異なる使い方となりますが、異常発振しなければ良しとします。

又、発振子メーカは、ICにはアンバッファタイプのインバータの使用を強く推奨しています。これについても、ここでは敢えて使用せず、NANDゲートにより実験しています。理由は発振ON/OFF制御を行いたいためです。

R2の値を変えた時のAおよびB点の波形を下表に示します。C1とC2は何れも120pFです。

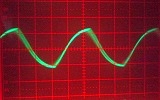

A及びB点の波形その1

(C1=C2=120pF、RL=∞)

V : 1V/div、H : 500ns/div

測定項目 R2 記事 10kΩ 5.1kΩ 2.7kΩ 周波数 MON 454.571 kHz 454.660 kHz 455.173 kHz 波形 MON

AMON

B

入力側であるA点においてほぼサイン波に近い波形となることが確認できました。(このことは上記の*印で示したトラ技やwebに記載があります。)

出力側であるB点においてもサイン波に近い波形が得られています。R2の値が大きいほどきれいなサイン波に近づきますが、振幅は小さくなります。

波形を見ると、A点の方がB点より多少綺麗に見えます。

R2を小さくするに従い、A,B点の振幅は何れも大きくなりますが、A点は2.7kΩ位から下がり始め(上の写真)、2.4kΩ以下で異常発振しました。確認のため実験ボードを2セット制作し、ゲート、発振子の交換やC,R定数変更を行いましたが、R2=0で正常発振することはありませんでした。異常発振となるR2の最大値はICや発振子のバラツキにより変わります。

又、R2の変化により、発振周波数も多少変化しています。(R2↓で周波数↑)

C1の値を変えて発振周波数を変化させた時のA点及びB点の波形の振幅を下表に示します。R2は5.1kΩ,C2は120pF、何れも固定です。

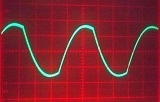

A及びB点の波形その2

(R2=5.1kΩ、C2=120pF、RL=∞)V : 1V/div、H : 500ns/div

測定項目 C1 記事 390 pF 120 pF 30 pF 周波数 MON 453.427 kHz 454.660 kHz 456.371 kHz 波形 MON

AMON

B

A点の振幅は、発振周波数が高くなる(C1小)程振幅が大きくなります。但し、C1=10pFでは異常発振しました。

一方、B点の振幅は、発振周波数が高くなる(C1小)程振幅が小さくなり、波形の上下に角ができて矩形波に近づきます。

C1=390〜30pF時の振幅変化はA点よりB点の方が小さいことが分かりました。上表から、C1=390pFの最大振幅に対するC1=30pFの振幅差を計算すると以下となります。

「MON A」 ・・・ 約+9.5dB

「MON B」 ・・・ 約−3.9dB

尚、この後の「NAND-BFO回路」において、C2を小さくする程変化が少なくなることが分かりました。例えば、C2約80pF、発振周波数454.0〜455.8kHzにおいて、B点における変化は約1dBです。

上表のC1=30pF、「MON A」測定時は、プローブ10pFの影響があるためC1=18pFにより測定しました。

「A点」は周波数変更による振幅変動が大きいため、今回は、「B点」における接続負荷の影響についてのみ調べました。実験回路のRLの抵抗値を変えて「MON B」の波形を測定しています。

B点における負荷RL の影響

(C1=30pF、C2=120pF、R2=5.1kΩ)V : 1V/div、H : 500ns/div

測定項目 RL 記事 7.5 kΩ 22 kΩ ∞ ( open ) 周波数 MON 456.516 kHz 456.367 kHz 456.371 kHz 波形 MON

B

C1は、発振周波数の高い方で異常発振しやすいため、高い方のC1=30pFとして測定しました。

RLを小さくする程振幅は小さくなります。RL=7.5kΩで測定はできましたが、それ以下では異常発振しました。

実験により、以下のことが分かりました。

1)74HC00による455kHzセラミック発振回路には、異常発振防止用抵抗が必要。

2)A、B点何れもサイン波形に近い波形が観測される。

但し、周波数固定の場合、波形はA点の方がB点より多少綺麗に見える。

3)発振周波数を変化させた場合、B点の方がレベル変化が少なく、可変幅がとれる。

但し、波形は共振周波数から離れるほど崩れる。

4)発振子への励振レベルがR2と接続負荷RLで分圧されるため、RLを小さくすると発振不安定の方向となる。

B点の接続負荷RLは、マージンを見込んで20kΩ以上とする必要がある。

5)B点からサイン波を取り出す場合には異常発振防止用抵抗の調整および実験による確認が必要。

実験では、R2=5.1kΩが得られた。

B点は、R2を大きくする程きれいなサイン波となりますが、異常発振あるいは発振停止しやすくなります。

このためR2の値を決定する際には、電源起動/停止、電圧変動や簡易な温度変動試験を行い、安定して発振すること確認する必要があります。目安として、455kHzセラミック発振回路ではおおよそ5kΩ前後、4MHz水晶発振回路ではおおよそ1kΩくらいとみています。(値はメーカが推奨するHCU04の値を参考にすると良く、大きく外れることは無い様です。)

NANDゲートによるセラミック発振回路からのサイン波取り出しに関する結論です。

1)取り出し箇所 : 周波数可変に対して振幅変動が少ない出力側(B点)から取り出すのが良い。

2)異常発振防止用抵抗 : 必須。値は概ねメーカが推奨するHCU04等の値とする。

3)B点の接続負荷 : 発振の安定性からできる限り高い方が望ましい。

4)具体例

<74HC00による455kHzセラミック発振回路の場合>

(1)異常発振防止用抵抗・・・5.1kΩ

(2)B点の接続負荷・・・・・・・20kΩ以上

トランジスタおよびFETを使用した回路例を示します。何れも、455kHz周波数固定です。

トランジスタによるサイン波取り出し回路例(455kHz)

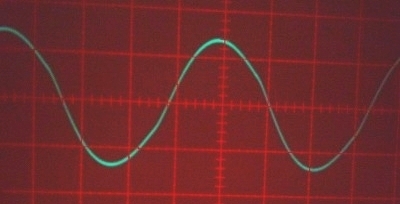

V : 500mV/div、H : 500ns/div

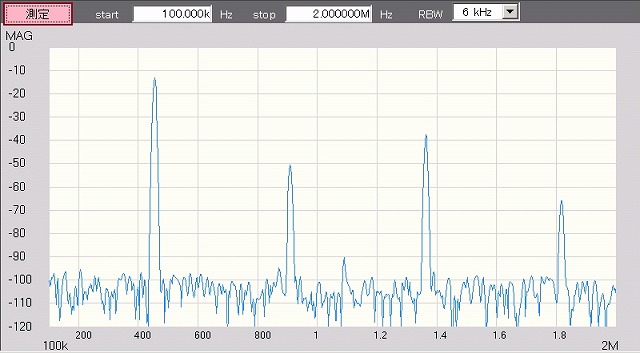

「OUT」出力波形(1.2kΩ終端)

2f=-37dB , 3f=-25dB , 4f=-52dB

FETによるサイン波取り出し回路例(455kHz)

V : 500mV/div、H : 500ns/div

「OUT」出力波形(1.2kΩ終端)

2f=-49dB , 3f=-28dB , 4f=-55dB

NANDゲートによるセラミック発振回路のゲート出力側からサイン波を取り出す実験と回路例を紹介しました。発振回路にICゲートを使用し、同調回路やLCフィルタ等、インダクタを使用することなく無調整でサイン波を取り出すことができるため、再現性が高い回路と云えます。

周波数可変については「NAND-BFO回路」を参照願います。