TS-520 VFOの発振周波数および可変幅の変更方法について述べています。

バリコンへ直列にコンデンサCsを追加する昔から採用されている方法です。各バンド、C容量はほぼ一定とし、インダクタンスは大幅変更となります。

TS-520 VFO(*1)の発振周波数変更についてはこれまでと同様、『帰還コンデンサC7およびC8には手を加えない』 ことで話を進めます。(一度手を付けると泥沼にはまることが目に見えていますので、今後も手を付けないことにしています。)

この前提条件の下で行った前回までの実験では2つの問題が発生しました。

一つは、発振周波数が基準のTS-520 VFO5MHzから離れるほど発振しづらいあるいは停止する現象です。この問題は直列コンデンサCb (C5およびC6) の容量増で対処できることが分かっています。

2つ目の問題は変更作業量の問題です。前回の変更では可変範囲を狭めたこと(例えば7MHzで680kHz→400kHz程)によりコンデンサ合成容量が2倍以上に増大しました。これにより、発振停止対策のためのCb調整に加え、発振周波数変更のための追加コンデンサの決定、実装・調整が必要となり、作業が煩雑となっていました。

今回は、この2つ目の問題である作業簡素化のため、

1) バリコンへ直列にコンデンサCsを追加することで、

(1)バリコンの仕様を変更することなく、共振回路のC0を任意に設定できることを示します。

(2)このことを利用し、C0を各バンド共にTS-520 VFO発振回路のそれに近い値に設定して極端な容量増を回避します。

2) 設計、改造、実験

上の方法を利用した設計例を示し、実機改造、調整手順について述べ、実測値と設計値を比較します。

*1:VFO UNIT (X4-1070-00) 回路図はここの「kenwood」から「TS-520」を参照して下さい。

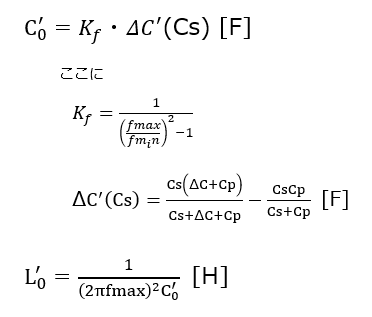

前回、発振回路の合成容量C0を求める式を示しました。その式をfmaxとfminで表される定数Kfとバリコン容量変化分ΔCとの乗算で表わすと以下となります。

C0 = Kf・ΔC ( Kfはfmax、fminで表される定数。詳細は省略。 )

今回はこの式から得られるC0を固定ではなく任意の値が得られる様、ΔCを変更可能とします。

その方法としてバリコンに直列にコンデンサCsを追加します。Csを追加することで、Cs=0〜∞に対してΔCは0から47pFまでの値をとることができます。従って、Csの値を変えることよってC0(=Kf・ΔC)は、Kfの0から47倍までの値を取ることができます。

(尚、Kfは、発振周波数が低いほど、又、可変幅が狭いほど大きくなります。)

今回はこのことを利用し、3.5~10MHzバンドへの発振周波数および可変幅変更に際し、Csを調整することでTS-520 VFOのC0近傍値に設定して調整を簡素化しています。

最終的に発振回路のCおよびL値を求める式が必要となりますので、話が少々長くなりますが簡単な式を用いて以下に述べます。

まず、バリコンの等価回路を示し、次に、LC共振部の回路とC0、L0を求める式を示します。

バリコン容量の最小値と最大値をそれぞれCminおよびCmaxで表すと、その差ΔCは

ΔC=Cmax-Cmin

Cp=Cminとし、ΔCとCpでバリコンの等価回路を表すと図1となります。(図中、Cp名称「残留分」は仮称です。)

図に示す通り、バリコンは変化分ΔCと残留分Cpの並列接続として表すことができます。

----------------------------------------------------------------------

<例>TS-520 VFOの場合

実測値Cvmax=58.7pFおよびCvmin=11.7pFにより、

ΔC=47pF

Cp=11.7pF

----------------------------------------------------------------------

図1と同様に、バリコンへ直列にコンデンサCsを接続した場合の等価回路を表すと図2(a)となります。

今後の共振回路の合成容量計算を簡単にするために、図1と同様にΔC'とCp'で表すと同図(b)となります。

ΔC'およびCp'は、以下の通り、Csを変数とする関数として表わされます。

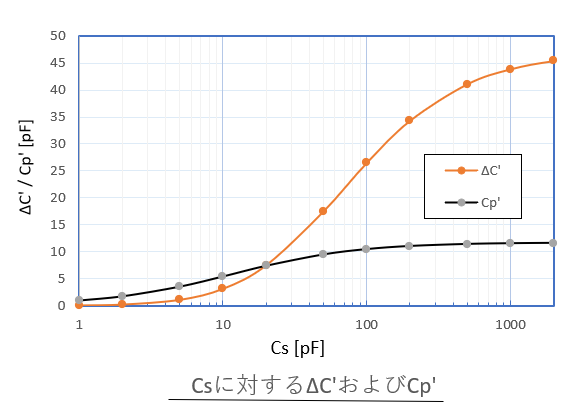

参考まで、ΔC=47pF、Cp=11.7pFの時のCsとΔC'およびCp'の関係を下図に示します。

Csが大きくなるほどΔC'、Cp'カーブはそれぞれ47pFおよび11.7pFへ収束していきます。

バリコン ( ΔC=47pF、Cp=11.7pF ) へCsを追加した場合のΔC'の上限および下限を求めると以下となります。

Cs→∞ (ショート)の時、△C'はΔC ( =47pF )

Cs→0 (オープン)の時、△C'は0pF

以上から、変化分ΔC'は、Csによって0〜ΔC[pF]の範囲で任意に設定することができます。

このことは、バリコンそのものを換えることなく、ΔC'をCsによって決定できることを示しています。

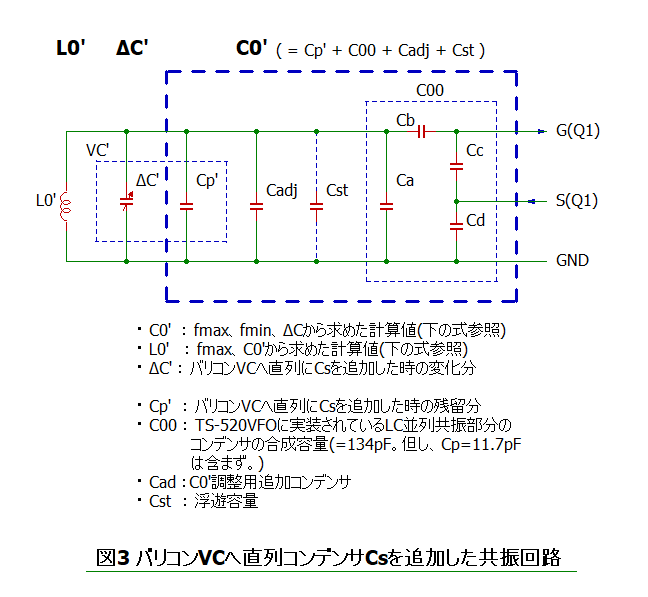

バリコンへ直列にCsを追加したTS-520 VFO (変形クラップ発振回路) LC共振部の回路を下図に示します。FETゲート-ソース間容量、ゲート−ドレイン間容量およびFETソース接続先の負荷容量は無視しています。VC’はバリコンVCへ直列コンデンサCsを追加した場合の等価回路(図2(b))で表わしています。

C0’は、下の「C0'、L0'を表わす式」のC0'式から得られる計算値です。この設計値C0'と実機上のコンデンサ (Cp'、C00、Cadj) および浮遊容量Cstとの関係は下式で表されます。

C0’ = Cp' + C00 + Cadj +Cst [F]

Cp'はバリコンへ直列コンデンサCsを追加した場合の残留分であり、Csの値によって決まります。C00はTS-520 VFOの実装コンデンサの合成容量(=134pF。詳細はここ) 、Cadjは調整用追加C、Cstは浮遊容量です。

つまり、元々実装されているTS-520 VFOのコンデンサを変更することなく、C00へCp'、CadjおよびCstを追加した値を計算値C0'と等しくすることにより、設計値fmaxとfminを実現することができます。

fmaxとfminからC0'とL0'を得る式を以下に示します。

バリコンへ直列コンデンサCsを追加したTS-520 VFO発振回路のコイルをL0'、合成容量をC0'およびバリコンの変化分をΔC'とすると、最高発振周波数fmaxと最低発振周波数fminは、それぞれ、以下の式で表されます。

上の2式からC0'およびL0'を求めると以下となります。

C0'式に着目します。

C0'は定数KfとCsを変数とするΔC'との乗算で表わされます。

C0'は、fmax/fminが小さい程、すなわち可変幅を狭くする程大きくなります。(別の見方をすると、ΔC'小程、C0'は大きくする必要があります。)

一方、fmax、fminが定まると、C0'は、Csを変更することによってΔC'=0〜ΔC(*)の範囲で任意の値を設定できます。( * : このΔCはTS-520 VFOのバリコンの変化分でΔC=47pFです。)

以上、任意のfmax、fminに対して、容量の異なるバリコンへ置き換えることなく、Cs追加・調整によってC0'をTS-520VFOのC0に近づけることができることを式で示しました。

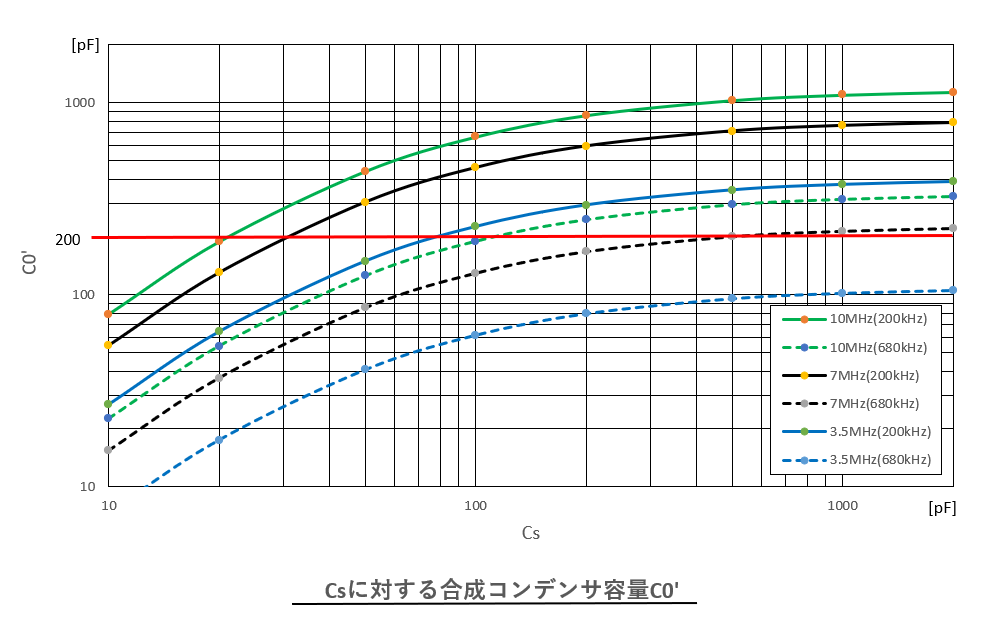

3.5、7および10メガバンドの周波数可変幅200kHzおよび680kHzについて、CsとC0'の関係を下図に示します。図中( )内は周波数可変幅です。各バンド共カーブ実線は可変幅200kHz、破線は可変幅680kHzです。

発振周波数と可変範囲によりますが、C0'を200pF (赤線) 付近とした場合、Csは約20pFから600pF前後となります。3.5MHz(680kHz)はCsを大きくしてもC0'=200pFは実現できませんが、Cs無限大(ショート)、C0'=100pF少々で可能です(但し、L0'はかなり大きくなりL0'=13.6μH程度)。

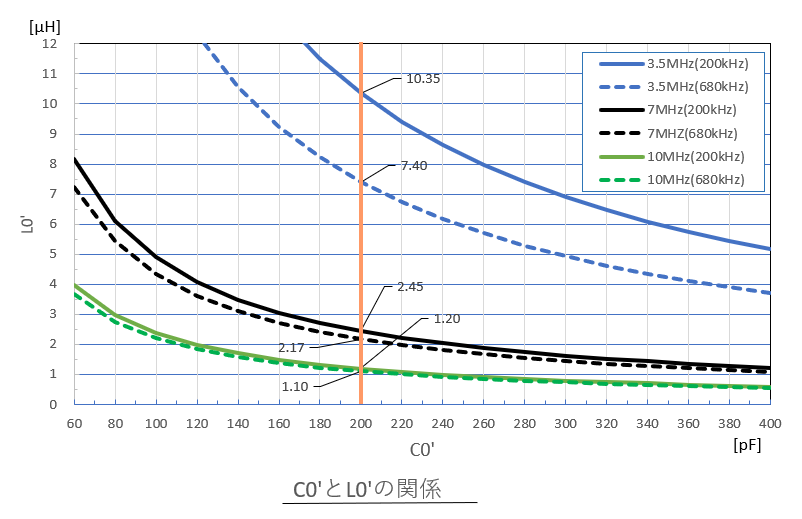

下表はC0'とL0'の関係を示した図です。

周波数可変幅200kHz〜680kHzの場合、3.5MHz(680)を除く、3.5MHz〜10MHzの全てのバンドにおいてC0'=200pF (橙線) 前後でL0'変更で対応可能です。この時、L0'はTS-520 VFOのコイルのボビンで実現可能なL0'=1.1~10.3μHの範囲に収めることができます。

コイルについては、TS-520 VFOのコイルを流用した場合、3.5MHz帯は巻数追加あるいは巻直しが必要で、7MHz、10MHz帯は巻数を減らす必要があります。7~8μH以上では恐らく巻き直しが必要で、現状(0.75Φ?)より細い0.3~0.4Φの線材が必要となります。

7MHzで現ボビンを巻数変更なしで使用するにはC0'=100pF前後とする必要があります。

設計例を示す前に、以下の3点について記しておきます。

1)発振可変範囲

2)温度変動

3)Cs温度変動が発振周波数に及ぼす影響

発振範囲は以下の2種のダイヤル機構に対して操作性を考慮して決めました。

1)TS-520VFOのギヤ機構・・・400kHz〜680kHz

2)バーニアダイヤル・・・・・200kHz

TS-520 VFO発振回路のコイルのインダクタンスおよびコンデンサの容量変更は、改造前の温度補償バランスを確実に崩します。ここでは詳細検討は行いませんが、回路図から読み取れる内容を独断と偏見で記します。

TS-520 VFOのC0を表す式の各部品記号横に温度係数を示す色を表記すると以下となります。Cc=C8およびCd=C7はマイカコンデンサ(恐らくSOSHIN製)であり、「CM93F2A151J」の「F」は温度係数0~70ppm/℃と思われます。

C0 = Cp+C00+Cst

C00 = {Ca=TC1(TYP)+C1<橙>+C2<赤>+C3<橙、赤、黒>+C20<黒>}

+ {(Cb=C5<赤>+C6<赤>),Cc=C8,Cd=C7の直列接続}

上式からわかることは2つあります。

一つはC1、C2およびC3が温度補償のメインで、部品リストではC3は調整用です。ほとんどこの3つのコンデンサでLの温度変動を打ち消しているようです。

2つ目は直列コンデンサCb=C5赤+C6赤、Cc=C8およびCd=C7です。Cbの赤は、Cc=C8、Cd=C7の直列接続されたマイカコンデンサの正の温度係数を相殺しているように見えます。Cb=C5+C6=47+22=69pF(-80ppm/℃)、C8とC7の直列C=75pF(おそらく+70ppm/℃)でほぼ相殺できています。

尚、RIT回路もC4緑で接続され、この先にバリピコがあり、これらの温度変動込みで全体のバランスをとっているようです。

以上から、大まかにTS-520 VFOの合成容量C0の温度係数を計算してみます。RIT回路接続は無しとします。また、直列コンデンサCb、Cc、Cdの温度係数は0とし、浮遊容量Cstは無視します。

C0 = 11.7+(11.1+47<橙>+15<赤>+15<赤>+10<黒>)+{(47+22),150,150の直列接続}+0

= 145.7[pF] (-65ppm/℃)

TS-520 VFO使用のコイルの温度係数は不明ですが、計算した温度係数はかなり小さ目の値となりました(*)。何処かミスがあるか、または、TS-520 VFOのボビン(直経14mm、材質セラミック)と太目の線材使用により低い温度係数を実現しているのかもしれません。

*:コイルの温度係数

JG3ADQさんのHPによると、7Kコイルのボビンで+200ppm/℃程度ではないかとのことです。

共振部のCsを除くコンデンサとコイルによる温度補償バランスが取れているものとし、Csのみの温度変動を仮定して周波数変動を検討しました。

Csの温度変動を10ppm/℃と仮定し、電源ONからケース内周囲温度10℃上昇、その後±1℃の変動有りとします。

<例>下の表1第7項(10MHz帯)

・電源ONから10℃上昇・・・・fmax -65Hz、fmix -270Hz

・その後±1℃変動・・・・・・fmax -(65±7)Hz、fmin -(270±27)Hz

Csは温度変動0(黒)を使用することで上の例の変動の1/10となることから、Cs温度変動による周波数変動への影響は実用上問題無しと判断します。

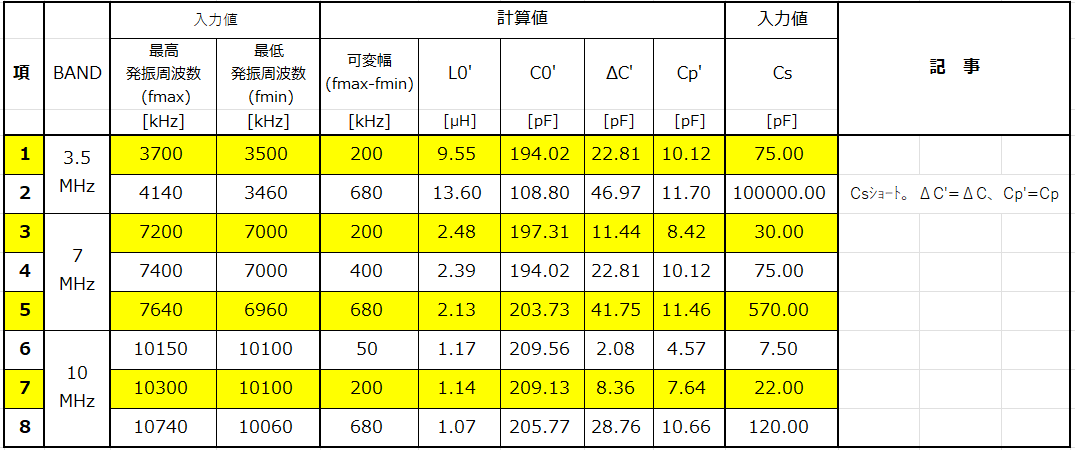

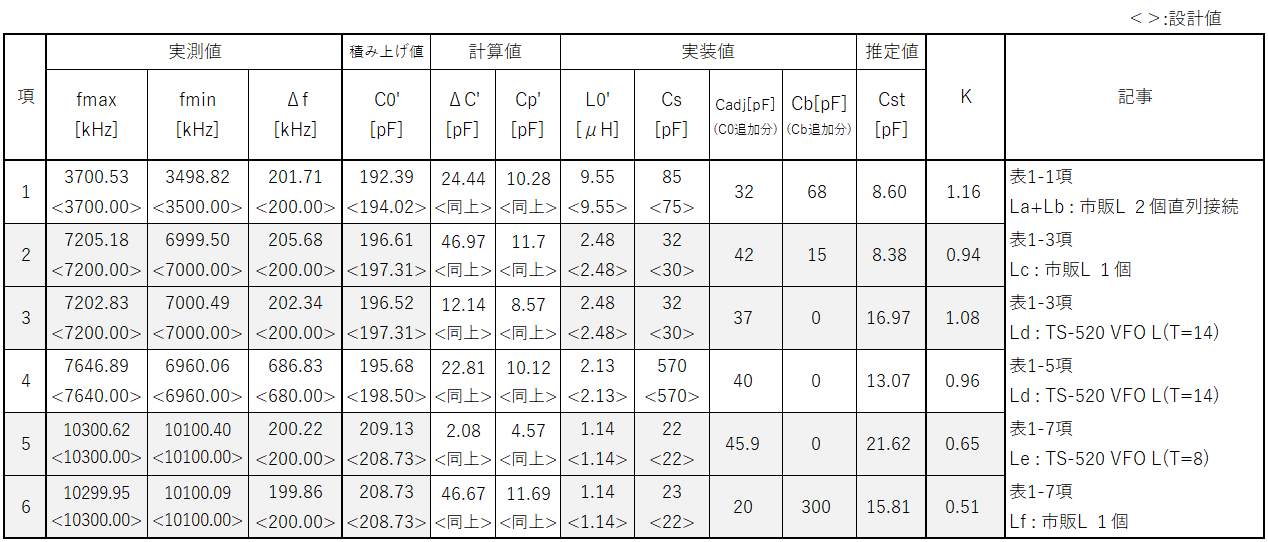

表1に設計例を示します。

表中の計算値は次の通り求めています。

まず、fmax、fminを与えて可変幅を固定し、次にCsを与えてΔC'、Cp’を求め、最後にC0'とL0'を計算しています。

表1 設計(例)

表中のL0'、C0'、ΔC'およびCp'の計算式はここを参照して下さい。

表から、与えられたfmax、fmin、可変幅に対してCsを適当に与えることにより、C0'をTS-520 VFOのC0=156.97pFを多少超えた200pF前後の値に設定しています。

2項のCs=0.1uFは実質∞であり追加無し(ショート)です。C0'=153.43pFがTS-520VFOの156.97pFを超えていませんが、改造はCadj値がマイナスとなり並列コンデンサの容量を減らす方向で容量変更または削除となります。

下の「実験」では、表の1、3、5および7項を取り上げ、実機により、Cb、Cadjの決定、Cstの推定を行います。

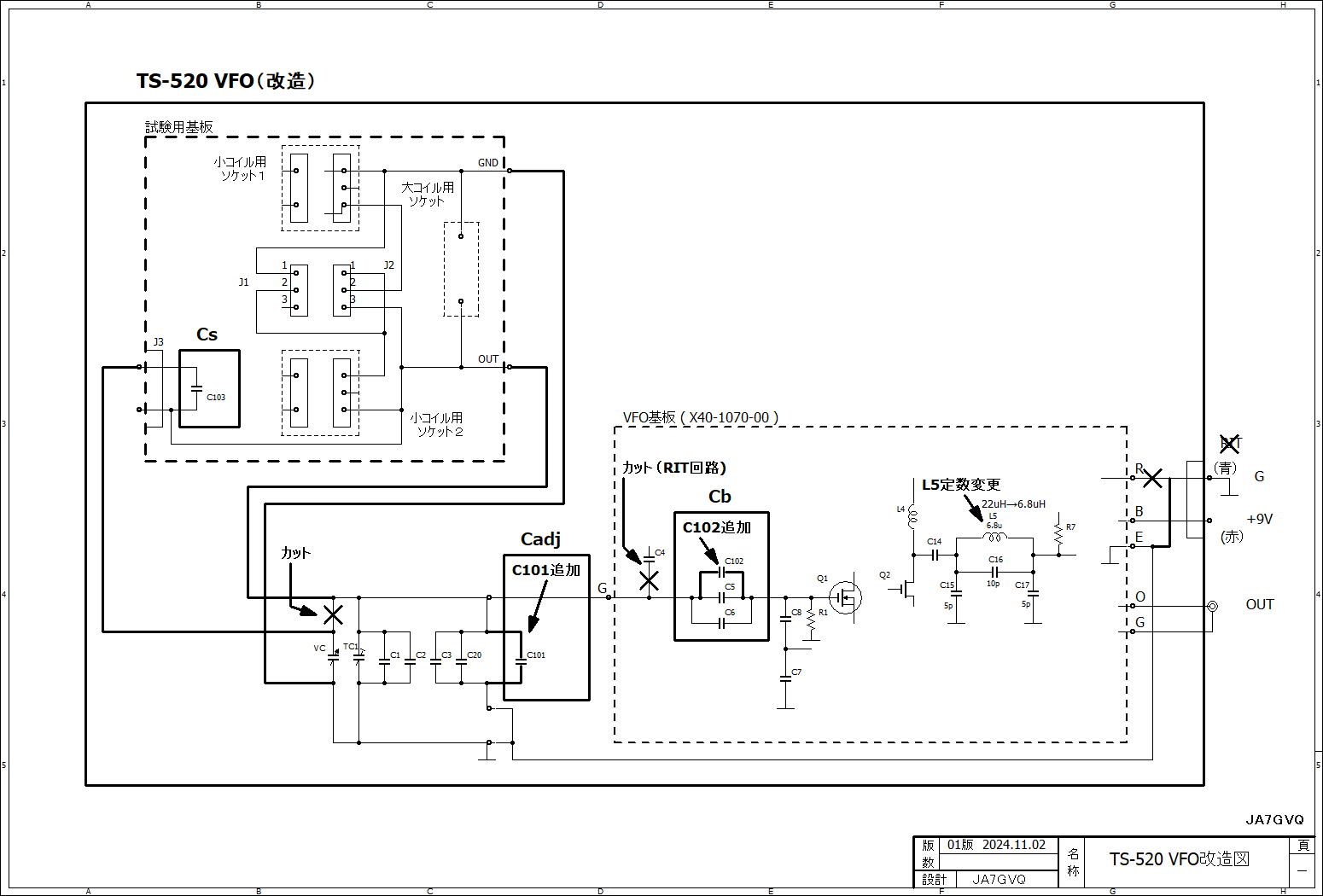

実験用回路図です。

太い波線内は実験用に追加した基板です。

VFOに以下の改造を行いました。1)〜3)は「TS-520 VFO周波数変更その1」を参照して下さい。

1)RIT回路切り離し・・・・C4リード線カット

2)フィルタ変更 ・・・・・C16を5pFへ変更

3.5M〜10MHz実験のためフィルタ回路のカットオフを7MHz用に改造

3)ダイヤル回転方向の変更・・・バリコンのストッパー(ネジ)を外す。

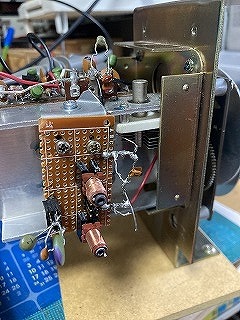

4)試験用基板製作

コイルおよびVCへの直列コンデンサを実装するための基板

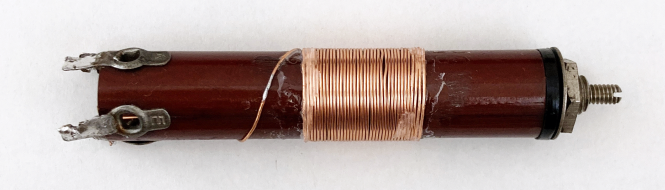

5)試験用コイル製作

いろいろなコイルで実験できるように試験用基板をコイルを外して実装しました。

バリコンへ直列追加するコンデンサCSも実装できます。

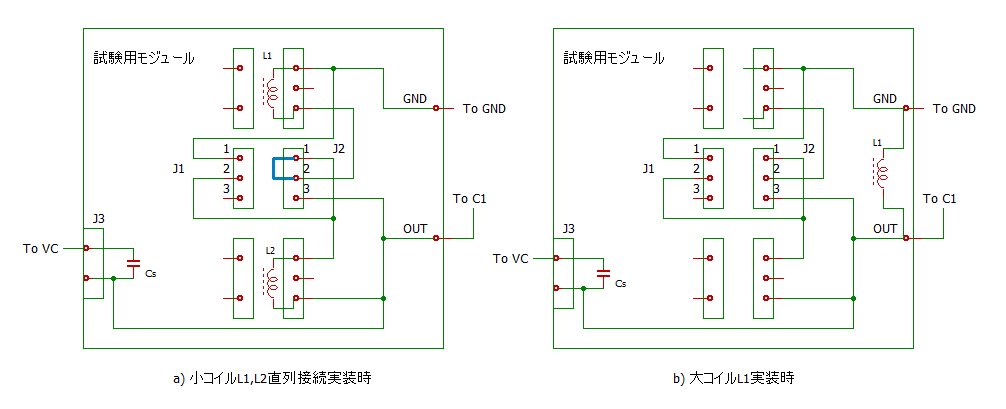

下図は、a)小コイル2個を直列接続、b)はTS-520VFOのL1と同サイズのコイルを実装した場合の接続例です。

a)は3.5MHzバンド、b)は7MHzおよび10MHzバンドの試験に適用しています。

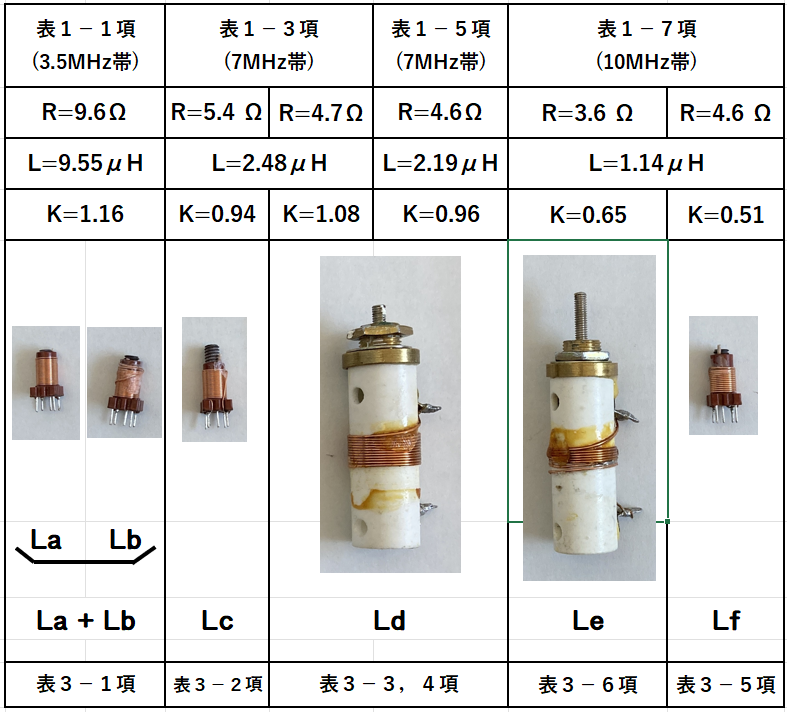

試験用コイルを下表に示します。測定はnanoVNA-H4で行いました。表中のRはコイルの損失分で、測定周波数は表1の対応する項のfmaxの値としています。

表2 試験用コイル

表中、LaおよびLbは市販品(*1)で2個直列接続で表1-1項の9.55μHを実現しています。TS-520VFOコイルではスペース不足により必要な巻数まで巻くことが出来ませんでした。

Lcは表1-1項のLa、Lbと同一品でコアを調整して2.48μHを得ています。

LdはTS-520 VFOコイルの巻数を減じてT=24として2.48μHを得、コアを調整して2.19μHを得ています。

LeはTS-520 VFOコイルの巻数を減じてT=21とし、コアにより1.14μH調整しています。

また、LfはLa,LbおよびLcとは別の市販品(*2)で、コアを調整して1.14μHを得ています。

インダクタンスの小数点2桁目は実際には測定機による変動があります。

表中のKはK=K'/Ktsであり、K'=L/R、Kts=L0/R0=0.86、L0およびR0は以下に示すTS-520VFOの実測値です(*3)。

L0=5.26uH

R0=6.13Ω

K≧1およびK<1であっても1に近い値なら発振起動 ( Cb増不要 ) が期待できます。

*1:Aliexpressから購入。26t、2.1〜6.3μH

*2:Aliexpressから購入。12t、0.6〜1.7μH

*3:この値は実測値であり、メーカ公開データではありません。

表2のコイルを使用し、表1のコンデンサ容量、周波数範囲が得られるか実験により確認します。

調整手順を示し、その手順に従って3.5MHzバンドの調整します。

7MHzと10MHzについては結果のみを示します。最後に3バンドの結果を表にまとめ、考察を行います。

なお、発振出力は出力端子へオシロ及び周波数測定器を接続して確認しています。

実機による調整手順を以下に示します。コイルの抵抗分は不明(測定していないもの)として進めています。

(【Step9】は、表3をエクセルを用いて必要な計算ができることを前提として話を進めます。)

【Step1】 コイルを実装し、未接続状態でインダクタンスを測定する。値が表1の通りとなるように調整する。

【Step2】 表1のCs値のコンデンサをバリコンへ直列接続。バリコンを最大にし、電源ONで発振するか確認する。

【Step3】 発振しない場合、Cbを追加し安定発振する値を探り、決定する。

【Step4】 バリコン最小に設定する。fmaxを測定し、表1のfmaxを超えて発振していることを確認する

【Step5】 Cadjを追加して発振周波数を表1のfminにできる限り近づける。

【Step6】 TC1により発振周波数を調整して表1のfminと一致させる。

【Step7】 バリコンを最大、最小にし、それぞれfmin、fmaxを測定し、仕様を満足することを確認する。発振範囲が狭い時はCsを大きく、広い時は小さくする。

【Step8】 fminをTC1により調整する。

【Step9】 Cstを把握するため表2を使用する。実機で得られたCb、Cadj値を表2へ与え、fnax、fminが表1の値となるようCst入力値を調整し、Cstを把握する。

【Step1】 コイルを実装し、未接続状態でインダクタンスを測定する。値が表1の通りとなるように調整する。

2つのコイルを試験用基板に実装し、直列接続となるようJ2 1-2間をショートしてインダクタンスを9.55uHへ調整します。

【Step2】 表1のCs値のコンデンサをバリコンへ直列接続。バリコンを最大にし、電源ONで発振するか確認する。

セラコン75pFをJ3へはんだ付けし、電源をONして発振するか確認します。

【Step3】 発振しない場合、Cbを追加し安定発振する値を探り、決定する。

発振しない場合は150pFを実装して発振することを確認します。その後、発振起動しなくなる値まで容量を下げ、最終的にその2倍の容量とします。

33pFなので約2倍の68pF(黒)としました。

【Step4】 バリコン最小に設定する。fmaxを測定し、表1のfmaxを超えて発振していることを確認する。

バリコンを最小に設定し、周波数を測定します。その周波数が表1のfmax=3700kHzを超えていることを確認します。

【Step5】 Cadjを追加して発振周波数を表1のfminにできる限り近づける。

Cadjを追加実装して3500kHzにできる限り近づけます。20pF(黒)と22pF(黒)を追加しました。

【Step6】 TC1により発振周波数を調整して表1のfminと一致させる。

TC1を廻して3500kHzへ合わせます。

【Step7】 バリコンを最大、最小にし、それぞれfmin、fmaxを測定し、仕様を満足することを確認する。発振範囲が狭い時はCsを大きく、広い時は小さくする。

バリコンが最小、最大の時、それぞれ、3700kHzおよび3500kHzとなることを確認し、変化幅200kHzに対して狭い場合はコンデンサを追加、超えている場合は75pFから徐々に減らして最終的に200kHzとなるようCsを調整します。

10pF(黒)追加しました。

【Step8】 fminをTC1により調整する。

fminを3500kHzとなるよう調整します。

【Step9】 Csを把握するため表2を使用する。実機で得られたCb、Cadj値を表2へ与え、fnax、fminが表1の値となるようCstを調整し、Cstを把握する。

実測データを下表に示します。「積み上げ値」C0’は図3に示す波線内の合成容量です。ΔC'とCp'は表1の値を転記しています。

表3 実測データ

概ね設計値通りであることが確認できました。但し、半数の3例が発振せずCbを追加しています。この発振停止問題については後述します。

<Csについて>

・1〜3項のCsは設計値より大きめ、特に低いバンド3.5MHzでは10pF増加となりました。

・第4項のfmax,fminおよびΔfにおいて6.8kHzの誤差が出ました。

この誤差は調整精度の問題であり、チタバリを並列実装して調整することにより誤差を減らすことができたと思われます。

<Cbについて>

・市販コイルを使用した場合は全てCb容量追加が必要ですが、TS-520VFOのコイルボビンを使用した場合は全て追加不要でした。

・第2項と第3項は表1の第4項、同様に、第5項と第6項は表1第7項についての測定結果です。

何れも市販コイルを使用した場合Cb追加が必要となっています。

<CbとKを比較>

・K大程Cb追加不要となることを期待していましたが、必ずしも関連性があるようにはみえません。

・例えば2項と5項を比較すると、K値は2項が1に近いにも関わらずCb追加が必要となっています。

・更に、周波数の低い第1項3.5MHzバンドにおいてもKが最も大きいにも関わらずCb追加が必要となっています。

バリコンに直列にコンデンサCsを追加することにより

・バリコンそのものを交換すること無く

・希望するfmin、fmaxを指定することで、C0'とL0'をそれぞれの式 (上のC0'式およびL0'式) により得られる

ことを実験により確認しました。

測定データが得られてほぼ設計値を満足することが分かりましたので終了するつもりでしたが、発振有無とRおよびKの関係についてどうしても腑に落ちない点があり、以下の「発振停止問題」について調査を続けることにしました。

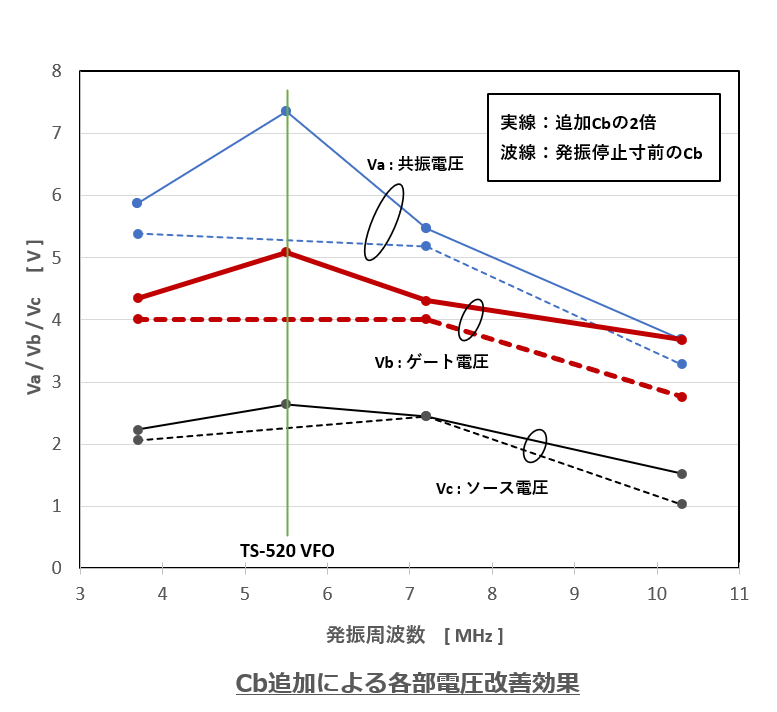

改造による発振停止問題について調査しました。

まず、状態把握のために発振停止によりCb追加が必要となった回路の各部電圧を測定しました。

下図に測定結果を示します。

横軸は周波数で、3.5、7、10MHzの各バンド1例を取り上げています。3.5MHzバンドは表3-1項、7MHzバンドは表3-2項、10MHzバンドは表3-6項、5MHz台は基準のTS-520 VFOです。

図の波線は、発振停止状態からCbを追加して発振停止寸前まで復旧させた状態の各部電圧で、実線は追加分Cbを更に2倍した正常発振状態の値です。

Vaは共振電圧、Vbはゲート電圧、Vcはソース電圧を示します。

これらの測定は通常のプローブを使用したデジタルオシロで値は画面表示された数値o-p値を読み取りました。プローブ容量の影響により測定値は実際より低下することは承知の上で傾向を観るために敢えてこの状態で測定しています。(ただし、10MHzバンドはプローブの影響が大きいためFETプローブと100kΩを直列接続して測定し、測定値は補正しています。)

7MHz Vcを除き、どのバンドの実線カーブも波線カーブより電圧が上昇しており、Cb追加による改善効果が認められます。

Vaは、5.6MHz基準から周波数が高くなるにつれて電圧が低下していますが、これは共振時の共振回路のインピーダンスZ=L/CRで (ほぼ) C一定の下ではLが小さくなるためです。

しかし、何故か、L大により共振電圧高くなる筈の3.5MHzバンドにおいても各電圧が大幅に低下しています。コイルは2個直列接続でL=9.55μH、R=9.6Ωですが、KはK=1.16でTS-520 VFOコイルより条件は良いはずです。

原因不明のまま、とりあえずコイルの内部抵抗を疑い、自作することにしました。

ボビン径12mm、線材ポリウレタン線0.4mmΦ、巻数35回。インダクタンス9.55μH、抵抗分6.0Ω(at 3.5MHz)でK=1.85です。

実装して確認したところ、Cb追加無しであっさりと発振しました。Va=7.6V、Vb=6.0V、Vc=5.4Vで5.6MHz基準の値より大きくなっています。(実際には飽和しているかもしれません。)

結局、コイルの内部抵抗 ( 前回9.6Ω、今回6.0Ω ) が大きいことが発振停止の原因のようです。

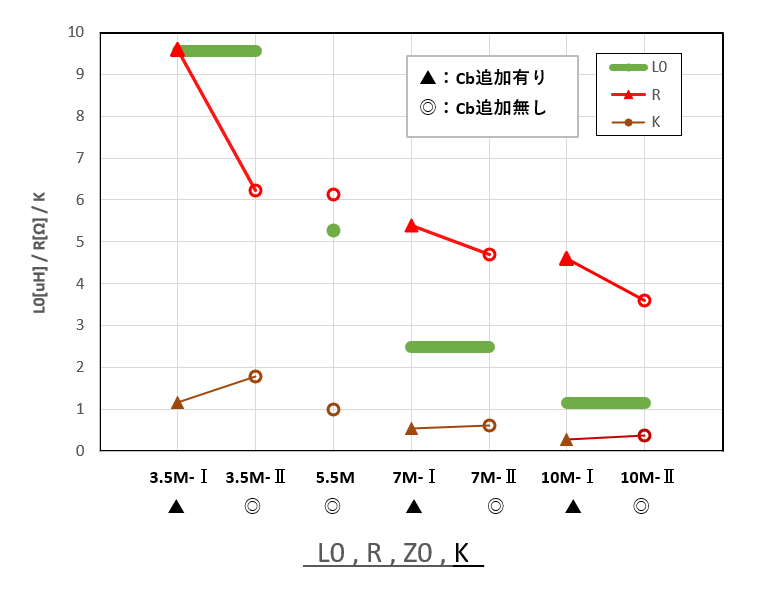

そこで、各バンドのCb追加有りと無しの回路のL0、R、およびKについてグラフにしてみました。▲印はCb追加無しでは発振せず、Cb追加した回路です。◎印はCb追加無しで発振した回路です。

グラフを観て驚きました。KとRの値の大小に関係なく発振するケースとしないケースがあります。特に、最も重要な指針と考えていたKが全く当てになりません。

今回の改造は、帰還コンデンサC8およびC7を変更しないだけでなく、共振回路としてのC容量も各バンドほぼ同一にしています。それらを踏まえた上で考えると、発振するかしないかはKやRの大小で決まるものではなく、その発振周波数におけるリアクタンス ( L、各Cの関連性は不明 ) の下でRの大小によって決定されているようにみえます。

例えば、3.5MHzバンドでは周波数、L一定の下でR=6.0Ωから9.6Ω間の何処かに発振限界点があり、同様に10MHzバンドではR=3.6Ωから4.6Ω間に限界点があることを示しています。

この現象を理解するためには、コイルの内部抵抗Rも含めた共振回路 ( 帰還伝送路網 ) と増幅回路との関係を表現した発振条件式が必要です。

発振の起動条件はNorCal 40A資料の”startup condition”(*1)に示されています。ただ、この式は増幅回路と帰還コンデンサのみで表現されRが出てきません。更に周波数に依存しない式となっています。

発振起動だけでなく、その後の発振を持続するための条件式をweb検索したところ3件ヒットしましたが、そのうちの1件(*2)について紹介します。

記事の回路は真空管回路によるクラップ発振回路の等価回路です。発振条件式を以下に示します。 ( Lに並列コンデンサが無く変形クラップ回路とは異なりますが参考になります。)

R = -gm・X2・X3 (*2)

Rはコイルの損失抵抗、gmは真空管のgm、X2およびX3はC2およびC3のコンダクタンスです。共振時ということでLとC1はこの式 ( 実数部 ) には表れません。

式の説明によれば、Rより式の右辺が小さいと発振せず、右辺がRより大きい場合回路は発振し、グリッド電流が増加してRと一致する方向へgmが低下して左右の値が一致した点で安定発振するとのことです。

上式は、発振するかしないかはRの大小だけではなく、gmの他、発振周波数、C2およびC3が関係していることを示しています。

この式は、まさしく上のグラフを観て感じた事そのものを指しているようです。

この式はエネルギーの消費と供給の関係を示したものです。Rの限界点を調べるためには共振電圧を与えて共振電流の下限を示す必要がありそうですが、難しそうなので他のアプローチを考えてみます。今の世の中シミュレーターが普及していますので、使用デバイスのデバイスモデルがあればLTSpiceによる回路シミュレーションによって大凡の傾向は掴めるかもしれません。

などとお茶を濁したところで、今回の調査はこの辺で終わりとします。

●結論

今回は、発振停止の原因となるRの限界点を探る式を得るところまではいきませんでしたが、発振するかしないかはAppendix(*2)の発振条件式からR、gm、発振周波数および帰還コンデンサC2、C3が関係することが分かりました。

*1 : 「Lecture24:Oscillators. Clapp Oscillator. VFO Startup」 Keith W. Whites

*2 : 「The Clapp Oscillator - and How! February 1953 QST」 www.rfcafe.com Rex Cassey*、ZL2IQ

Cb追加による改善について簡単に記述しておきます。

Cb追加によりリアクタンスが下がり、電流が増加することでゲートーソース間電圧egsが上昇します。それによりIdが増加し、結果ソースから帰還コンデンサC3 (TS-520 VFOではC7) へ流れる電流、つまりコイルへの供給電流が増加することで共振電圧が上がり、発振が持続します。

ここでは帰還コンデンサの値を変更しないことを前提として進めてきていますが、バンド毎に帰還コンデンサも含めてL、C値を決めている記事がありましたので、参考までに載せておきます(*1、*2、*3)。*2はG3OOUさんのオリジナルでNE602で使用した値、*3ではその値をOK1IKEさんがトランジスタ回路へそのまま採用しています。

*1 :「The Field-Effect Transistor as a Stable V.F.O Element」 P.11 G. D. Hanchett. W2YM

*2 :「Progressive Receiver Design - Direct Conversion Receiver / Product Detector」 Bob F Burns G3OOU

TS-520 VFOの発振周波数を3.5MHz帯、7MHz帯及び10MHz帯へ変更するコイル及びコンデンサの変更について記載しました。

この話の切っ掛けは、TS-520VFOを利用して再生式受信機を制作する際、バーニヤダイヤルを採用するために容量変化分47pFのバリコンでバンド幅200kHzをカバーする (発振可変幅を狭める) ことが必要となり、その解決のためにバリコンに直列コンデンサCsを追加したことから始まりました。

検討を進めると、CsはC0大となる課題解決策としても使えることが分かり、おかげでVFO発振停止問題をCb調整のみで解決する方法を確立することができました ( 大袈裟です (_ _;) )。

この結果を参考にしてバーニヤダイヤルを使用した7MHz再生式受信機を制作する予定です。