TS-520用VFO(5MHz帯)の発振周波数を変更する実験です。

< 目次 >

・はじめに

・ダイヤル1回転当たりの周波数変化

・fmax、fminを与えてL0、C0を求める

・設計目標

・C0変更

・実験(3.5MHz帯)

・変更後の実測値と目標値を比較する

・回路の浮遊容量

・Cb指標について (試案)

・Cb、Cc、Cd変更について

・おわりに

TS-520 VFO (変形クラップ発振回路) の発振周波数を変更する実験を行いました。

ここでは発振回路のコンデンサ変更に関する記載のみとし、他の関連箇所変更詳細については「TS-520VFO 周波数変更その1 (改造編)」を参照願います。

この5MHz台を発振するVFOは、当時の国産アマ機製造有名メーカの一つである「TRIO」製であり、発振条件、発振起動、安定性については十分余裕を持った設計が成されているものと考えます。

そこで、後述する直列接続Cc、Cdを固定した状態で、5MHz台から周波数1/2〜2倍程度の変更なら、それほど苦労することも無く周波数変更することができ、性能的にも十分使えるのものができるのではないかと考え、実験してみることにしました。実績のあるしっかりした製品だからこそ安心して取り組むことができると云えます。対象バンドは3.5MHz帯、7MHz帯および10MHz帯です。

共振回路のLとCを求める式において、fmax、fminを指定することでダイヤル1回転当たりの周波数変化も得られるようにしました(*)。

式から得られるC0は、L0と並列のC(以降Ca)と3個の直列接続C(以降、Cb、Cc、Cd)の合成値であり、これらへ適度に配分する必要があります。その中で、並列共振回路ーFET回路間のCbについては値を実験で探りました。Cc (ゲートーソース間) 及びCd (ソース-グランド間) は変更しないこととしました。Cc、Cdを変更することなく、正常に発振するCb値を実験により求めたことになります。

実験によりCaおよびCbの追加C値を得ることができ、安定して発振することを確認しました。また、設計目標の各項目について測定を行い、目標値と実測値が一致することを確認しました。ここでは3.5MHz帯の実験について記載しています。

実験中、回路の浮遊容量らしき存在を確認しました。これによる問題は特にありませんが、今回の変更に当たり無視できない事象のため調査内容を記載しました。

Cb決定のための実験を不要とするCb指標について記載しています。理論に基づかない、実験値と根拠のない係数から作った試案です。

最後に、今回の3.5MHz帯以下及び10MHz帯以上の変更時に必要になると思われるCc及びCdの変更について、留意点を記載しています。

*:「設計パラメータにfmin、fmaxを含めて発振周波数のL、Cを求めたい。」ことからweb検索したところ、「Gan's blog - フーラム」さんの"Re: VFO"がヒットしましたので参考にさせて頂きました。

TS-520 のVFO UNIT(X40-1070-00)の回路図は他のwebを参照して下さい(BAMA等)。

TS-520VFOのダイヤル1回転当たりの周波数変化は20kHzです。

(PLL方式等デジタル処理へ移行後は10kHz/回転の機種が多いようです。)

ダイヤル目盛りは600kHzの幅があるため目盛りの端から端まで30回転となります。

目盛りの外側両端まで含めると34回転であり、以降ではこの34回転で話を進めます。

1回転当たりの周波数変化dは次式となります。

d=(fmax-fmin)/34 [Hz/回転]

周波数変化dは、d=20kHz/回転では広過ぎるため、今回はd=10kHz/回転前後を目標とします。

今回のVFO周波数変更 (改造) に当たり、このパラメータを設計に盛り込みたいと考えました。つまり、発振周波数の最大値と最小値を与えてd値をコントロールしたいということです。

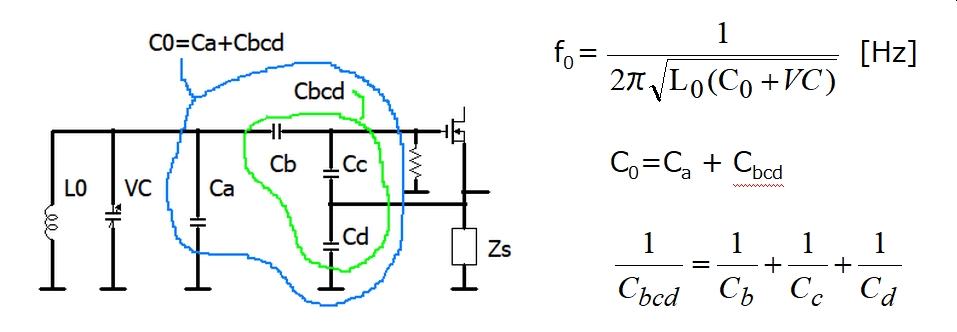

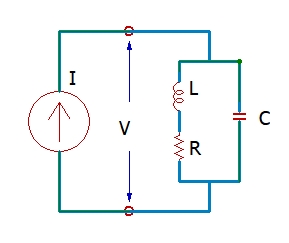

変形クラップ発振回路の発振周波数f0を表す式を下図に示します。 図中、C0はCaとCbcdの並列接続値、CbcdはCb、Cc、Cdの直列接続値です。

バリコンVCの値によりf0が変化します。

以下では、式簡略化のためこのVCを固定値ΔCへ置き換えます。

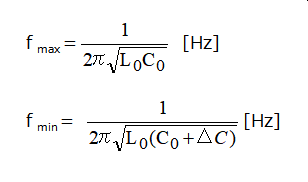

最高発振周波数fmaxと最小発振周波数fminを、それぞれ、次式で表します。

ここで、ΔC=(バリコン最大値-最小値)です。最小値分はC0へ含めました。

上の2式からC0及びL0を求めると、それぞれ、次式となります。

上の2式により、fmax、fminおよびΔCを与えることで、C0とL0を求めることができます。

周波数可変範囲はfmax-fminです。

各バンドへ周波数変更するための目標とする設計値を下表に示します。

設計目標値

3.5MHz帯L0は、調整中コアネジ先端を欠損したため5.39μH固定としています。尚、可変幅は3.805MHzまでの305kHz幅をカバーできていません。コイルの巻数を増やすことで可能ですが、今回は現状コイルで可能な最大周波数としました。

C0を求めた結果、3バンド共に、変更前5MHz帯の値147pFから2倍以上と、大幅に追加することになりました。

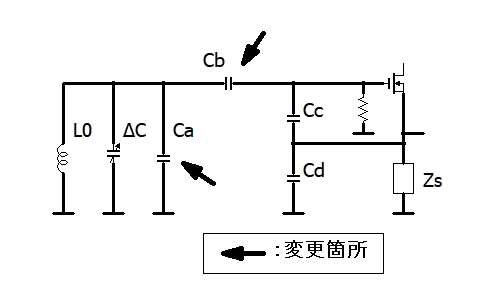

変更箇所

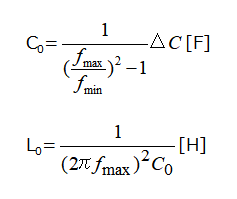

コンデンサの変更箇所を下図 (左) に示します。

変更対象はCaとCbです (参考:*) 。CcとCdは対象外とします。

「改造仕様」表中のC0は、C0=Ca+ (Cb、Cc、Cdの直列接続) です。

変更箇所 |

|

TS-520 VFOの部品番号および定数を上図(右)に示します。ここではQ1ソース出力側C9(=3pF)以降は無視しています。

TS-520 VFO部品番号との対応は以下の通りです。

L0=L1

ΔC=VC(MAX)-VC(MIN)=59-11.7=47.3pF (47pF)

Ca=VC(MIN)+TC1(TYP)+C1+C20+C2+C3=110.7pF (111pF)

Cb=C5+C6=69pF

Cc=C7=150pF

Cd=C8=150pF

ここに、VC(MIN)=11.7pF、VC(MAX)=59.0pF、TC1(TYP)=12.0pF。

又、Cbcd、C0は以下となります。

Cbcd=(Cb、Cc、Cd直列接続)=36pF

C0=Ca+Cbcd=147pF

変更対象Ca、Cbと対応するTS-520 VFOのCは、以下の通りです。

Ca → C1、C20、C2、C3

Cb → C5、C6

*:「高周波回路の設計・製作」 鈴木憲次 CD出版社 P.98〜P.99

C0のCaおよにCbへの配分決定のため、3つの実験を行いました。

1)実験a :Caのみ増加

L0と並列のCaのみ増加により、どこまで発振周波数を下げることができるかの実験です。

結果、目的の発振周波数まで下げることはできませんでした。

2)実験b :CaとCb増加

実験aの結果を踏まえ、Cbを段階的に増加させ、都度Ca増加により設計周波数まで下げることができるか実験しました。

結果、Cb増加により、設計周波数まで下げることができました。但し、Cb増加の上限制限条件は未調査です。

3)実験c : Cc、Cd増加

Cc、Cd増加により、発振可能周波数を下げることができるかの実験です。

結果、どの組み合わせにおいても、下げる方向とは逆の結果となりました。

1)実験a : Caのみ増加

VC最大(ΔC=47pF)、すべてのコンデンサ定数はTS-520 VFOから変更せず( Ca=111pF、Cbcd=36pF、C0=147pF )、コイルはL0=5.39μHとします。

この状態で、Caへ調査用バリコンCVを接続して3.5MHzで発振するか確認します (下図参照) 。

TS-520 VFOはC0(5MHz帯)=Ca+Cbcd=147pF。CV増加で3.5MHz発振した場合はC0(3.5MHz帯)=Ca+CV+Cbcd=338.0pFなので、CV=338-147=191pF付近となるはずです。

結果、調査用CV=191pF付近では3.5MHzで発振しませんでした。

VCを最大(ΔC=47pF)とし、発振状態から調査用CVを徐々に増やしていくと、ある点以降発振停止し、起動もしません。停止直前の周波数は3.5MHzより高い周波数です。この時、CV=137pF付近でした。

C0=147+137=284pFとなり、3.5MHz目標のC0=338pFまで達していません。

調査用CVを安定起動領域まで戻し (この時CV=134pF)、VCを廻して発振周波数範囲を調べると、

3.70MHz(fmin) 〜 3.95MHz(fmax )

となりました。目標最小周波数3.50MHz発振に対して200kHz高い方へシフトしています。

以上、並列コンデンサCaの増加のみでは3.5MHzでは発振しないことが分かりました。

<シミュレーションによる調査>

シミュレーションを行ったところ (*) 、Caを増加することによって5MHz帯回路に比して並列共振回路電圧が低下することが分かりました。これにより、増幅回路入力電圧が低下し、回路出力電流が減少 (発振強度低下)、発振起動停止に至ります。

又、Cbを増やすことにより増幅回路の入力レベルが増加し、発振起動しやすくなることを確認しました。

<結果>

以上から、Ca増のみでは目的周波数まで下げることができず、Ca増とともにCbも増加する必要があることが分かりました。

* : 以下を参考にクラップ発振回路をシュミレーションしました。

「コルピッツ発振回路」 CQ Connect 小川 敦

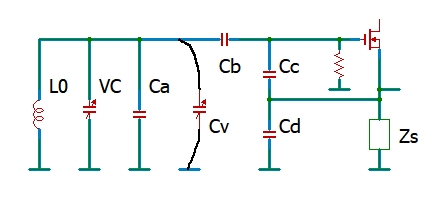

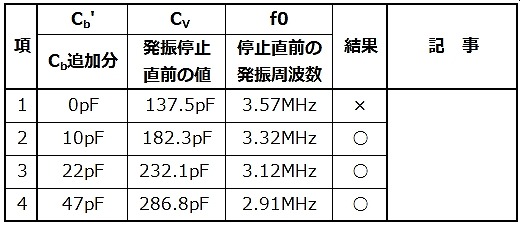

2)実験b:CaとCb増加

Cb(=69pF)へCb'を追加(パラ接続)した状態で調査用CVを徐々に増加し(Ca増加)、発振停止直前のCV値と発振周波数を調べました。

Cbコンデンサ追加

結果、Cbを増加することによって、最低発振周波数を3.5MHz以下にできることが分かりました。

次に、発振周波数範囲を調べました。

以下の表は、VCをmax固定とし調査用CV可変により最小周波数を3.50MHzへ調整、その後、VC可変により周波数範囲を確認したものです。発振範囲はいずれも目標値を満足しています。

Cb追加と発振周波数範囲

CVとCb'からC0を計算すると、設計値334.8pFとおおよそ34〜40pF程の差があります。この差は、前述の浮游容量とCv測定時のばらつきと考えられます。(実験時は浮遊容量の存在は頭の片隅にも無かったため、全く気に留めていませんでした。)

<結果>

Cb増加により、設計値C0を満足する値で発振することが分かりました。

但し、今回の実験では、Cb増加の上限条件の調査、実験まで踏み込んでいません。

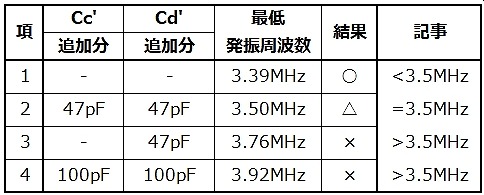

3)実験c : Cc、Cd増加

Cc(150pF)、Cd(150pF)は今回は変更しないことにしていますが、実験してみました。Cbは上の結果から22pFを追加しています。

コンデンサを追加した状態で調査用CV値を増加し、発振停止寸前の周波数を調べました。

Cc、Cdコンデンサ追加

第1項は3.5MHz帯への変更後の状態で最低発振周波数が3.5MHz以下を測定しています。

第2項Cc、Cd各47pF追加で3.5MHzで発振しましたが、不安定でした。

第3項はソース出力電流を増やすためCdのみ増加させ、Cv容量を減じて最低発振周波数を調べたところ、最低発振周波数は高くなっています。

又、第4項のCc、Cd増加では3.92MHzと最悪の結果となりました。

<結果>

Cc、Cd容量増で最小発振周波数が低くなることを期待しましたが、逆の結果となりました。

2〜3項全て、CbのリアクタンスXbに対してXc,Xdが低くなる方向のためゲート入力電圧が低下したのかもしれません。

シミュレーションしたところ、Ccは小さくすることでゲート入力電圧を上げ、Cdは大きくすることでソース出力電流を増加させることが分かりました。

今回はCc,Cd固定ですが、変更する場合はCbも含む変更が必要となるようです。

5MHzを基点として、それより低くなる程リアクタンス大となり、Xd大によりソース出力電流を低下させるためCd容量を大きくする必要があるようです。また、基点より高くなる程リアクタンス小となり、Xc小によりゲート入力電圧が低下するためCc容量を小さくする必要があるようです。

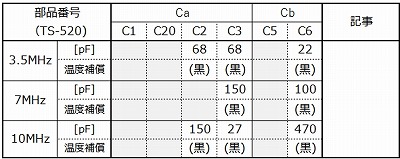

4)追加コンデンサ

各バンドの実験により決定したCa、Cb追加コンデンサの値を下表に示します。

Cbの追加コンデンサは、発振するギリギリの追加C値を安全のために2倍してE24系列の良く使われる値としています。

追加コンデンサ

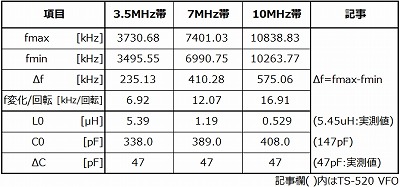

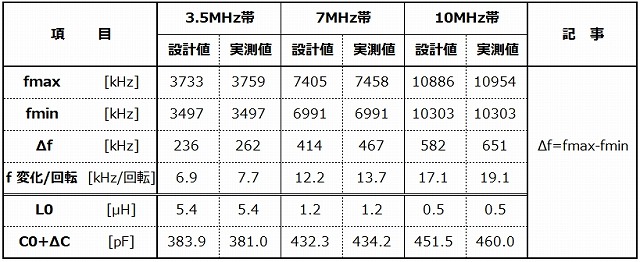

コイル、コンデンサ変更後の実験機の実測値を下表に示します。

(C0+ΔC)実測値は、L0を外した両端からnanoVNAにより測定した回路のCです (「回路の浮遊容量」参照) 。

比較のため設計値も載せています。設計値のfminは比較を容易にするため実測値へ合わせて再計算しています。

設計値と実測値

設計値と実測値でほぼ一致した結果が得られています。

fmax値は実測値より設計値が低いですが、これはVC最小値が実際は11.7pFより低かったのかもしれません。

10MHz帯追加コンデンサの容量決定作業の中で、実機上のC0値 (コンデンサ公称値で計算した合成地) が設計値C0と一致しないことに気が付きました。実機上のC0値が設計値C0より数十pF程低い値となります。

原因不明のため調査することにしました。

1)調査

C0が設計値と一致しない原因は、当初、回路の実装部品を疑いました。

そこで、原因特定のため、コンデンサ2〜3個の小区分に分けて切り離し、区間単位で測定して合計しました。しかし、その値は依然として設計値C0より大きく下廻ります。

原因不明のまま途方に途方に暮れていましたが、少区間単位ではなく、L0を除いた回路全体のCを測定してみることにしました。

Loを外し、その両端からVC最大時の回路の容量(=C0+ΔC)を測定しています。測定時の回路電源はONです。

測定器はnanoVNA、PCアプリはNanoVNASaverを使用し、回路のパラレルCを測定しています。

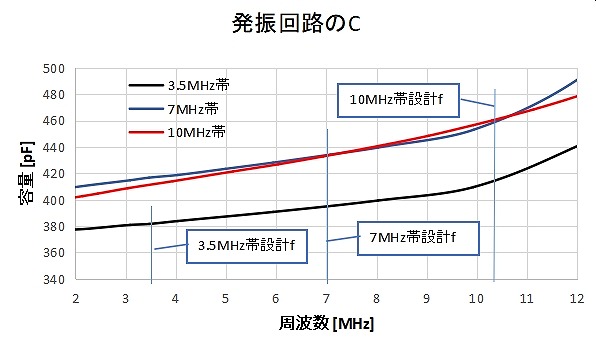

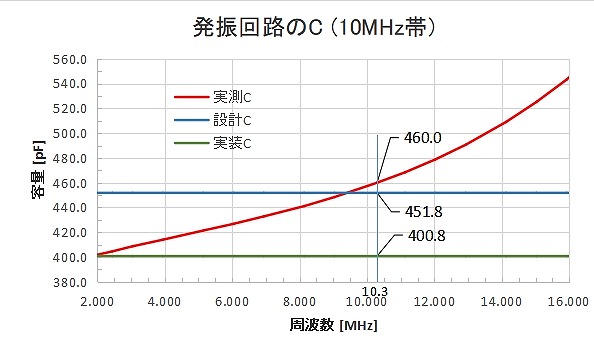

実測した回路のC特性を下図に示します。

設計周波数 (fmin) 付近における回路の実測値は、どのバンドにおいても、図には表示していませんが設計値にほぼ一致しています(設計値:以下の「設計C」参照)。

詳細を見るために10MHz帯を取り上げ、下図に実測カーブと設計値、実装値を示します。

図中、「実測C」、「設計C」および「実装C」は以下の通りです。

・実測C : 測定器(nanoVNA)により測定した回路のパラレルC成分

・設計C : fmin、fmax、ΔCから求めた(C0+ΔC)設計値

・実装C : 実機上のコンデンサ公称値で計算したC合成値(C0+ΔC)

上図から次のことが云えます。

(1)設計周波数 (最小発振周波数) 付近において、実装Cが設計Cに対して大幅に下回っている。しかしながら、実測した値 (実測C) は設計値 (設計C) とさほど変わらない。

→ 実装C=400.8pFに対し、実際に測定した値は実測C=460.0pFであり計算C=451.5pFに近接。実装Cに何らかの容量成分が相加されていると考えられる。実測C≠設計Cは測定誤差の可能性有り。

(2)回路のC(実測C)が周波数に対して右肩上がりのf特を有す。周波数によって変化する。

→ 単なる容量成分ではなく、CやVC以外の配線等によるL成分 (誘導性リアクタンス) も含まれる。

(1)および(2)から、設計Cと実装Cの差は回路の浮遊容量 (浮遊リアクタンス) と判断しました。

浮遊容量=設計C-実装C=451.5-400.8=50.7pF

少区間測定と回路C測定の違いは、後者は少区間同士接続の配線 (信号線、グランド線) の追加であり、この配線によるストレー容量が追加されたと考えます。

但し、下表の通り数十pFと値がかなり大きく、配線長による影響等詳細調査していないため浮游容量のみと断定して良いものか分かりません。

又、実測C≒設計Cですが、これは、測定誤差と実装コンデンサの公称値からのバラツキにより、実測Cにバラツキがあるためです。これにより、実測Cは設計C前後のバラついた値を示します。

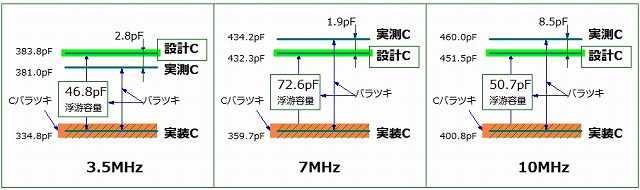

2)浮遊容量

各周波数帯の最小発振周波数付近の実測C、設計Cおよび実装Cを下表に示します。

発振回路のC

表中、「設計Cー実装C」は浮遊容量です。

7MHz帯の値が他バンドに比して突出しています、原因は分かりません。2台測定してほぼ同一の値であり、測定ミスではないようです。

上表の各Cの関係をわかりやすくするため図で表しました。

前述の反復となりますが、結論として、

(1)設計Cと実装Cの差 → 浮遊容量と考えるのが妥当

(2)実測Cが設計Cと一致しない → 実装Cのバラツキ、測定誤差が原因

3)浮游容量の影響

設計Cと実装Cの差が浮遊容量とするならば、その実態は部品間を接続する信号線とグランド(アース線も含めて)間やリード線も含めた部品自身のストレー容量であり、回路の静電容量の一部と考えて良く、それらを含めた発振動作に特に悪影響はありません。

ただし、浮游容量が全体容量に占める割合が大きく、かつ、浮遊容量変動要因(コイル、バリコン、コンデンサおよび配線材の機械的強度など)が存在すると無視できなくなると思われます。

(「浮遊容量」については、真空管時代の製作記事に良く記載されていた内容程度の知識しかありません。ほとんど忘れかけていた事象に遭遇して戸惑いました。)

実験によりCb値を得ましたが、任意周波数変更に対して計算で求めることが出来ないか検討しました。

基準となるTS-520 VFO (以降、基準5MHz VFO) のCb (以降、基準Cb) に係数を乗じて求める、その係数を求める式を作ることになります。式から求めた係数値と基準Cbとの積で得られるCb値は、この値でなければならないというこではなく、その値近傍なら使えるでしょうという目安となるようなものです。今後、係数に基準Cbを乗じたCb値を「指標」と呼ぶこととします。

今回の指標は理論から導き出したものではなく、実験から得られた値とラフな係数から作り出した式であり、あくまでも試案です。適用周波数範囲はおおよそ3MHz〜11MHzとしておきます。

バンド毎に、発振停止寸前のCb値を実験で得、それを2倍した値を目標値としました。これを元に、任意周波数に対して適用できるように一般化した式を作り、指標としています。

発振停止に至る原因はCa増加によりゲート入力電圧が低下するためと考え、基準Cb値からCbを増加する(リアクタンスを下げる)ことでゲート電圧を上げる、そのCb増加のための係数を求めることを考えました。

Ca増加により、共振回路の共振時のインピーダンス (つまり、電圧) が低下することに着目しました。基準5MHz VFOのインピーダンスとの逆数比をとることにより増加係数を得ることができます。しかし、発振回路の正帰還ループではなく共振回路単独での計算のため計算値のバンド間差が大きすぎます。そのため、解決策として数値を圧縮するための係数との積をとり、指標としました。この係数は、基準となる5MHzに対する各バンドの周波数比です。但し、周波数を取り上げた理論的根拠は全くありません。

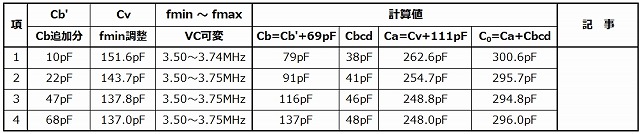

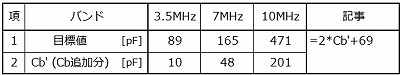

1)目標値

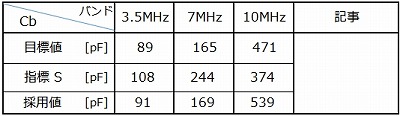

Cb指標の目標値を下表に示します。

Cb指標の目標値

第2項は、各バンドで実験した際に取得した発振停止直前のCb追加分です。

目標値は、このCb'を安全のために2倍した値を基準Cbへ追加した値 (=2*Cb'+69pF) としています。

以下では、この値へ近づけるための係数を求める式を示します。

2)並列共振回路

並列共振回路を下図に示します。コイルのESRのみ考慮に入れています。

共振時(ω=ω0)のインピーダンスZは、R≪ω0L、R2≪L/Cとすると、以下の式で表されます。

Z≒L/CR

この時の共振回路両端の電圧Vは以下となります。

V=Z・I

=(L/CR)・I

式より、VはLに比例し、CとRに反比例します。つまり、C増加によって共振回路両端の電圧は低下します。Lが小さくなることでもVaは低下します。Rは小さくなる程Vは大きくなりますが、無限に大きくなるわけではなく、Cの漏れ電流等によるパラレル抵抗分により頭打ちとなります。RはLの線材径、巻数により変わりますが、線材、形状に大きな差異がなければ巻数、言い換えればインダクタンスに比例すると考えます。

3)指標(試案)

以下にCb指標Sxを示します。

Sx = Kx・Cb5 [pF]

Kx=Kz・Kf・Kc

Kz = Zv / Zx:対象回路共振時のインピーダンスZxに対する基準5MHzVFO Zvとの比

Kf = fxmin / fvmin:基準5MHzVFO fmin=4.9MHzに対する対象fminとの比

Kc =1.1:補正係数

Zv = Lv / (Cv・Rv):基準5MHzVFO共振時のインピーダンス

=2.81×104Ω (但し、Rvは正規化値を使用)

Zx = Lx / (Cx・Rx):対象回路共振時のインピーダンス

Cb5=69pF :基準Cb

fxmin :変更発振周波数の最小値

fvmin=4.9MHz:基準5MHzVFO最小発振周波数

Lv=5.45uF :基準5MHzVFO共振回路のL0

Cv=194pF :基準5MHzVFO共振回路の(C0+ΔC)

Rv:基準5MHzVFO共振回路のLの等価直列抵抗 (=1:正規化)

Lx:対象共振回路のL0

Cx:対象共振回路の(C0+ΔC)

Rx:対象共振回路のLの等価直列抵抗 (Rvで正規化)

Rx、Rvは共振回路のコイルの内部抵抗です。但し、上の式ではRx、Rvの比率が分かれば良く、ここではRv=1とし、RxをLの比率に合わせます。

4)Cb値比較

目標値と指標S及び実際に採用した値を下表に示します。

Cb値比較

10MHz指標が374pFと低めに出ています。追加分Cb'は374-69=305pF、目標値の根拠としている発振停止直前の追加Cb値Cb'=201pFに対し1.51倍であり、根拠は無くいい加減ですが、実験時の感触から良しとします。

今回はCc,Cd固定としCbのみ変更しました。3MHz〜11MHzの範囲を超える変更を行う場合にはCc、Cdの変更も必要と考え、留意すべきC増減方向について備忘録として記載しておきます。

1)Cb

2つの変更要因がある。

(1) 並列共振回路の共振時のインピーダンス(両端電圧)に依存。基準5MHz VFOに対して、

a) 共振インピーダンスが低い場合

共振電圧低下によるゲート入力電圧低下改善のため、Cb容量を増加する方向。

b)共振インピーダンスが高い場合

Cb容量減の方向。ただし発振動作に問題なければ変更不要。

(2)変更周波数に依存 (下記Cc、Cdに関連)。基準5MHz VFOに対して、、

a) 周波数下げる場合

直列接続コンデンサCb、Cc、Cdのリアクタンス大となる。ゲート入力電圧不足の場合Cb容量増加する。

b) 周波数上げる場合

直列接続コンデンサCb、Cc、Cdのリアクタンス小となるが、Cbは特に変更不要。

2)CcおよびCd

変更周波数に依存する。基準5MHz VFOに対して、

a) 周波数下げる場合

Xd大によるソース出力電流低下改善のため、Cd容量を増加する方向。

b) 周波数上げる場合

Xc小によるゲート入力電圧低下改善のため、Cc容量を減ずる方向。

TS-520 VFOを改造し、発振周波数を3.5MHz帯、7MHz帯及び10MHz帯へ変更するコイル及びコンデンサの変更について記載しました。又、任意周波数への変更の際のCb値を得る指標(試案)を作りました。

3バンドの変更を行いましたので、今後、再生受信機やスーパー受信機に応用していく予定です。