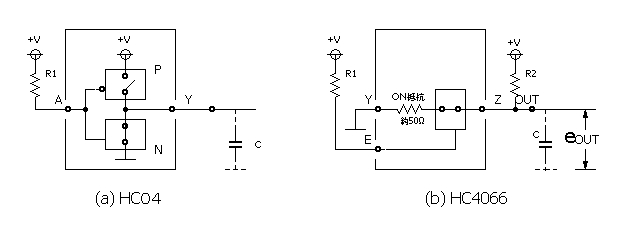

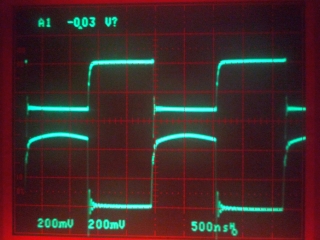

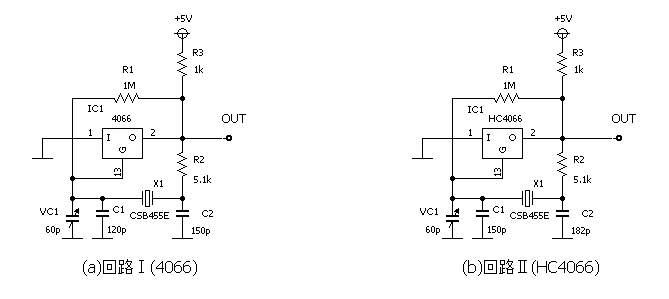

丂恾3-2(a)HC04偼擖椡A揰傪R1偱僾儖傾僢僾偟偰偄傑偡偺偱丄弌椡偼乭L"偲側傝丄A揰傪僌儔儞僪傊棊偲偡偲弌椡偼僗僀僢僠P傪捠偟偰乭H"偲側傝傑偡丅乭L"偐傜乭H"傊偺愗傝懼傢傝偼P,N偺僗僀僢僠儞僌懍搙偵埶懚偟丄崅懍偵愗傝懼傢傝傑偡丅偙偺帪偺Y揰偺棫偪忋偑傝摿惈偼奜晹偺C偲P丂MOS丂FET偺ON掞峈偵傛傞帪掕悢偱寛傑傝傑偡偑丄ON掞峈偼旕忢偵彫偝側抣偱偁傞偨傔崅懍偵棫偪忋偑傝傑偡丅

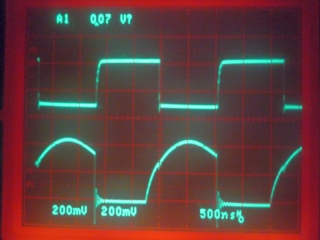

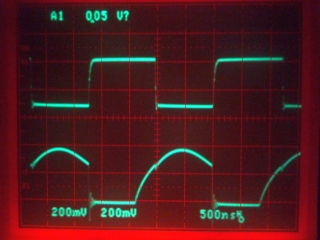

丂堦曽丄摨恾(b)HC4066偼丄擖椡E偑乭H"偱撪晹僗僀僢僠偑ON偲側傝丄傾僫儘僌擖椡Y偑乭L"偺偨傔弌椡Z偼乭L"偲側傝傑偡丅乮ON掞峈偲R2偵傛傞揹棳偵傛傝丄懡彮僌儔儞僪儗儀儖傛傝忋偑傝傑偡丅乯E傪僌儔儞僪傊棊偲偡偲撪晹僗僀僢僠偼僆僼偲側傝丄弌椡Z偼乭L"偐傜乭H"傊棫偪忋偑傠偆偲偟傑偡偑丄C偑懚嵼偡傞偙偲偵傛傝丄廩揹偟側偑傜棫偪忋偑傝傑偡丅偦偺帪娫偼R2偲C偺帪掕悢偵傛偭偰寛傑傝傑偡丅R2偑彫偝偄掱帪掕悢偼彫偲側傝棫偪忋偑傝偑憗偔側傝傑偡丅

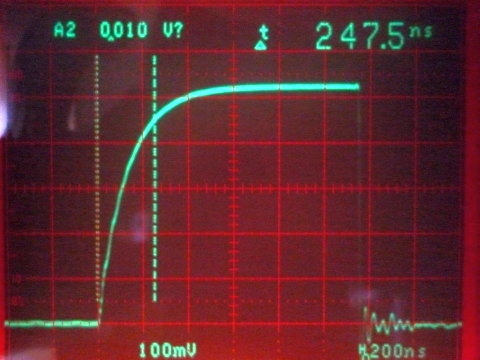

丂攇宍偺撦傝嬶崌偄傪寁嶼抣偲幚應抣偱堦抳偡傞偐妋擣偟偰傒傑偡丅恾(b)偺夞楬偺弌椡揹埑偼

丂丂丂倕out=V丒(1-倕-t/CR2)

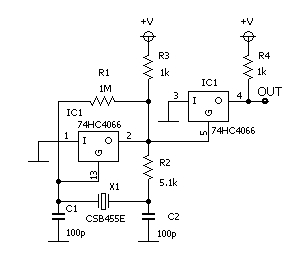

丂R2亖侾侽倠兌丄C=侾侽侽pF丄V=5V丄倲亖1.1侾兪s乮幚應抣丅恾3-1(a)嶲徠丅乯

丂丂丂倕out=V丒(1-倕-t/CR2)亖俁丏係[V]

丂恾3-1乮a)偱偼栺俁丏俀V偱偡偑丄傎傏堦抳偟偰偄傞偲傒偰椙偄偲巚偄傑偡丅俆V傑偱棫偪忋偑偭偰偄側偄偙偲偑暘偐傝傑偡丅

丂師偵丄R2亖侾倠兌丄C=侾侽侽pF丄V=5V偲偟偰丄俋侽亾棫偪忋偑傝揰偺帪娫倲乫偼

丂丂丂倲乫亖-C丒R2丒倢値乮侾-倕out/V)亖俀俁侽ns

丂幚應抣偼栺俀係俉兪倱乮恾3-2乮倐乯嶲徠丅乯偱偡偑丄傎傏堦抳偟偰偄傞偲傒偰椙偄偲巚偄傑偡丅

丂埲忋偐傜尨場偼丄傾僫儘僌僗僀僢僠弌椡夞楬偺僾儖傾僢僾掞峈偑戝偒夁偓傞偨傔偱偁傞偙偲偑妋擣偱偒傑偟偨丅

丂忋偺寢壥偐傜丄攇宍偺棫偪忋偑傝夵慞偺偨傔偵丄僾儖傾僢僾掞峈R4偼侾倠兌傪巊梡偡傞偙偲偵偟傑偟偨丅